Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

Unit 4th of the computer organisation and architecture student notes

Typology: Study notes

1 / 24

This page cannot be seen from the preview

Don't miss anything!

Input/Output Organisation: Peripheral devices, I/O interface, Asynchronous Data transfer, Modes of data transfer, Direct Memory Access, I/O processor. In addition to the CPU and a set of memory modules, another key element of a computer system is a set of I/O module. An I/O module is not just mechanical connectors that wire a device into the system bus but it contains some intelligence. That is contains a logic for performing a communication function between the peripheral and the bus. Owing to the following reason we need an I/O module: There are wide varieties of peripherals with variety of operation methods. It is impractical to incorporate the necessary logic within the CPU to control a range of devices. The data transfer rate of peripherals is often much slower than that of the memory or CPU. Peripherals often use different data formats and word lengths than the computer system to which they are attached. An I/O module has two major functions –

Among the most common peripherals are keyboards, display units, and printers. Perhaps those provide auxiliary storage for the systems are magnetic disks and tapes. Peripherals are electromechanical and electromagnetic devices of some complexity. We can broadly classify peripheral devices into three categories: Human Readable : Communicating with the computer users, e.g. video display terminal, printers etc. Machine Readable : Communicating with equipments, e.g. magnetic disk, magnetic tape, sensor, actuators used in robotics etc. Communication : Communicating with remote devices means exchanging data with that, e.g. modem, NIC (network interface Card) etc Block diagram of Peripheral device Control signals determine the function that the device will perform such as send data to I/O module, accept data from I/O module. Status signals indicate the state of the device i.e. device is ready or not. Data bits are actual data transformation. Control logic associated with the device controls the device's operation in response to direction from the I/O module. The transducer converts data from electrical to other forms of energy during output and from other forms to electrical during input. Buffer is associated with the transducer to temporarily hold data being transferred between the I/O module and external devices i.e. peripheral environment. Input Device Keyboard Optical input devices o Card Reader o Paper Tape Reader o Optical Character Recognition (OCR) o Optical Bar code reader (OBR) o Digitizer o Optical Mark Reader Magnetic Input Devices o Magnetic Stripe Reader o Magnetic Ink Character Recognition (MICR)

A mouse is also a pointing device. It is held in one hand and moved across a flat surface. Its movement and the direction of the movement is detected by two rotating wheels on the underside of the mouse. The wheels have their axes at right angles. Each wheel is connected to a shaft encoder which emits electrical pulses for every incremental movement of the wheel. The pulses transmitted by the mouse determine the distance moved. When a user moves the mouse across a flat surface, the cursor on the CRT screen also moves in the direction of the mouse's movement. By moving the mouse, user can point to a menu on the screen. By pressing the button on the mouse, the user communicates his choice to the computer. The mouse is also used to draw sketches, diagrams, etc. on the CRT screen, The mouse is also used to edit text. For editing a text on the screen the cursor is quickly moved to the desired point of the screen by moving the mouse. A mouse has one or more buttons on the surface for clicking and thus controlling the action. Output Devices : Output devices are used to transfer the information stored in the computer memory or the result of any processing done by the CPU to the outside world. There are many output devices manufactured for this purpose, but the most commonly used devices are the video monitors and printers. Printers provide a permanent record on paper.

1. Video Display Unit (VDU or Monitor) : A Visual Display Unit (VDU) is a device that displays text and graphics on a screen. It is commonly used in computers to display the output of the computer's processing unit, allowing the user to interact with the computer and see the results of their actions. The VDU consists of a screen, which is usually a flat panel display such as a LCD or LED, and a circuit board that drives the screen and processes the input and output signals. The screen is typically connected to the circuit board through a cable, and the circuit board is usually housed in a separate enclosure or integrated into the monitor itself. Monitors are available in 9", 12", 14", 15", 17", 19", and even in 21" size. Working of a Monitor : The main component inside a monitor is a picture tube or CRT (cathode ray tube). CRT is an evacuated glass tube, roughly conical in shape. It has a phosphor coating on the inside of the large screen end and an electron gun at the narrow end. (Fig 1) The electron gun fires a narrow beam of electrons at the screen and when this beam strikes the phosphor coating, light is emitted. Raster scan technique is adopted for generating images on the CRT display.

In this technique, horizontal and vertical deflection signals are generated to move the beam in forward and backward directions across the screen like a raster. The retrace portion of raster scan pattern is supperessed (blanked) by reducing the intensity of the electron beam during the time of retrace. The complete CRT screen can be considered to be made of thousands of dots, known as pixels (picture elements). Any pixel can be illuminated by the electron beam when it hits the pixel during the raster scan process or it can be blanked by reducing the intensity of the electron beam. On a standard monochrome monitor, the electron beam scans the screen 50 times per second. The phosphor has 'persistence', which means it keeps radiating light even after the electron beam has moved away. The scan rate and persistence of vision together enable the user to see a steady, flicker-free image. A monochrome monitor needs three signals to produce a display : a) Horizontal synchronization (HSYNC) to tell it when ascan line is about to begin. b) Vertical synchronization (VSYNC) to tell it when the display is going to start at the top of the screen. c) VIDEO which switches the electron beam ON and OFF. In addition a fourth signal (intensity) selects whether the displayed dots are dim or bright. The display adapter card generates these signals.

2. Printers : Printers are the most popular output devices. They provide information in a permanent readable form. They produce printed outputs of results, programs and data. A character printer prints one character of the text at a time. They are low – speed printers. Their printing speed lies in the range of 30-600 characters per second. The character printers can be classified as : a) Impact printers b) Non impact printers Imapct printers use an electro – mechanical mechanism that causes hammers or pins to strike against a ribbon and paper to print the text. Two types of impact character printers are available: dot matrix printers and letter quality printers. Non imapct printers do not use any electro – mechanical printing head to strike against ribbon and paper. They use thermal, chemical, electrostatic, laser beam or inkjet technology for

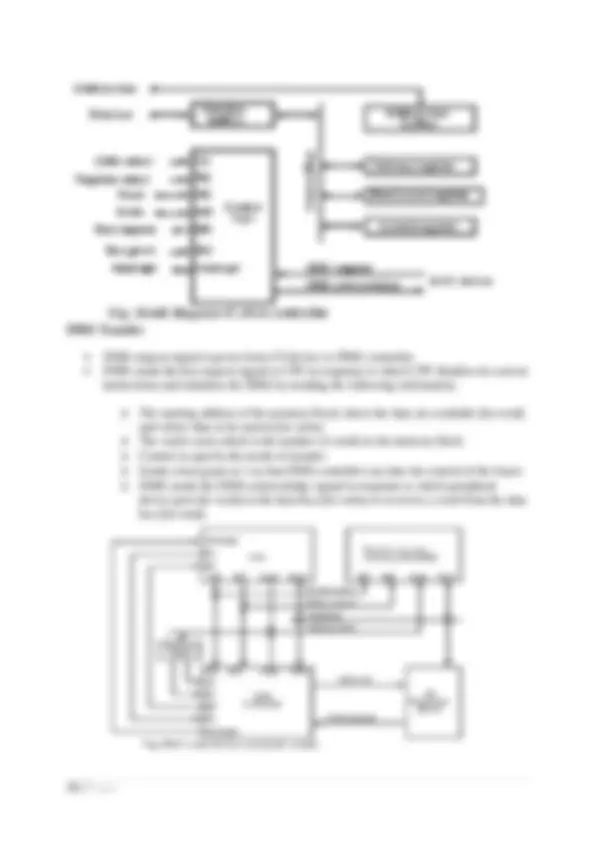

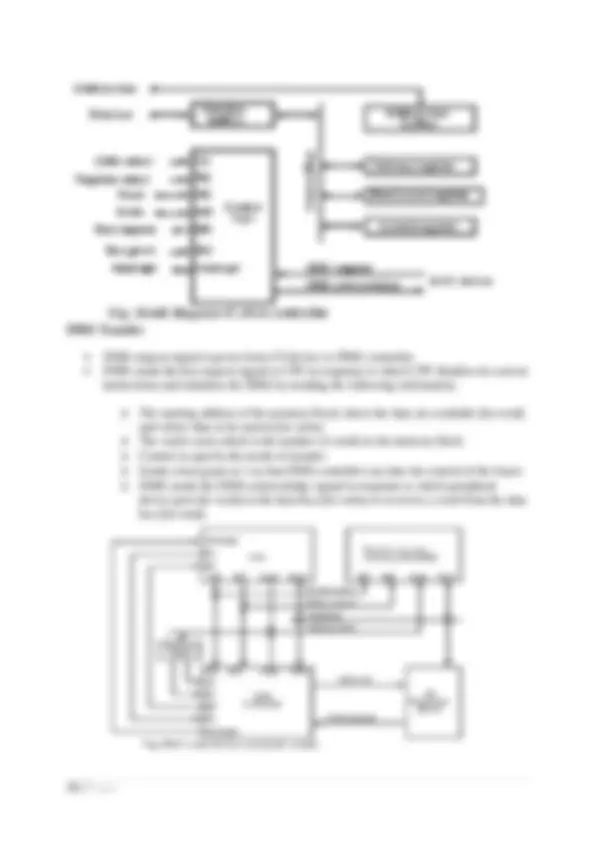

Peripherals often use different data format and word length than the computer to which they are connected. Thus an I/O module is required which performs two major functions. Interface to the processor and memory via the system bus. Interface to one or more peripherals by tailored data links. I/O Module Functions The I/O module is a special hardware component interface between the CPU and peripherals to supervise and synchronize all I/O transformation The detailed functions of I/O modules are: Control & Timing : I/O module includes control and timing to coordinate the flow of traffic between internal resources and external devices. The control of the transfer of data from external devices to processor consists following steps: o The processor interrogates the I/O module to check status of the attached device. o The I/O module returns the device status. o If the device is operational and ready to transmit, the processor requests the transfer of data by means of a command to I/O module. o The I/O module obtains the unit of data from the external device. o The data are transferred from the I/O module to the processor. Processor Communication : I/O module communicates with the processor which involves: o Command decoding: I/O module accepts commands from the processor. o Data: Data are exchanged between the processor and I/O module over the bus. o Status reporting: Peripherals are too slow and it is important to know the status of I/O module. o Address recognition: I/O module must recognize one unique address for each peripheral it controls. Device Communication : It involves commands, status information and data. Data Buffering : I/O module must be able to operate at both device and memory speeds. If the I/O device operates at a rate higher than the memory access rate, then the I/O module performs data buffering. If I/O devices rate slower than memory, it buffers data so as not to tie up the memory in slower transfer operation. Error Detection : I/O module is responsible for error detection such as mechanical and electrical malfunction reported by device e.g. paper jam, bad ink track & unintentional changes to the bit pattern and transmission error. I/O Module Structure : The I/O bus from the processor is attached to all peripheral interfaces To communicate with the particular devices, the processor places a device address on the address bus. Each interface contains an address decoder that monitors the address line. When the interface detects the particular device address, it activates the path between the data line and devices that it controls. At the same time that the address is made available in the address line, the processor provides a function code in the control way includes control command, output data and input data.

Fig: Block diagram I/O Module I/O Module Decisions Hide or reveal device properties to CPU Support multiple or single device Control device functions or leave for CPU Also O/S decisions o e.g. Unix treats everything it can as a file Interfaces Interface is a shared boundary btween two separate components of the computer system which can be used to attach two or more components to the system for communication purposes. There are two types of interface: CPU Inteface I / O Interface Input-Output interface Input-Output interface provides a method for transferring information between internal storage (such as memory and CPU registers) and external I/O devices. Peripherals connected to a computer need special communication links for interfacing them with the central processing unit. To resolve these differences, computer systems include special hardware components (Interfaces) between the CPU and peripherals to supervise and synchronize all input and output interfaces. The communication link resolves the following differences between the computer and peripheral devices.

the peripheral controller. It also conducts the transfer of information between peripheral and processor and also integrates the data flow. The I/O bus is linked to all peripheral interfaces from the processor. The processor locates a device address on the address line to interact with a specific device. Each interface contains an address decoder attached to the I/O bus that monitors the address lines. When the address is recognized by the interface, it activates the direction between the bus lines and the device that it controls. The interface disables the peripherals whose address does not equivalent to the address in the bus. Interface performs the following: o Decodes the device address (device code) o Decodes the commands (operation) o Provides signals for the peripheral controller o Synchronizes the data flow and supervises the transfer rate between peripheral and CPU or Memory An interface receives any of the following four commands − Control − A command control is given to activate the peripheral and to inform its next task. This control command depends on the peripheral, and each peripheral receives its sequence of control commands, depending on its mode of operation. Status − A status command can test multiple test conditions in the interface and the peripheral. Data Output − A data output command creates the interface counter to the command by sending data from the bus to one of its registers. Data Input − The data input command is opposite to the data output command. In data input, the interface gets an element of data from the peripheral and places it in its buffer register. Asynchronous Data Transfer Internal operations in individual unit of digital system are synchronized by means of clock pulse, means clock pulse is given to all registers within a unit, and all data transfer among internal registers occur simultaneously during occurrence of clock pulse.Now, suppose any two units of digital system are designed independently such as CPU and I/O interface. And if the registers in the interface(I/O interface) share a common clock with CPU registers, then transfer between the two units is said to be synchronous.But in most cases, the internal timing in each unit is independent from each other in such a way that each uses its own private clock for its internal registers.In that case, the two units are said to be asynchronous to each other, and if data transfer occur between them this data transfer is said to be Asynchronous Data Transfer. But, the Asynchronous Data Transfer between two independent units requires that control signals be transmitted between the communicating units so that the time can be indicated at which they send data.

This asynchronous way of data transfer can be achieved by two methods:

The Strobe Control method of asynchronous data transfer employs a single control line to time each transfer .This control line is also known as strobe and it may be achieved either by source or destination, depending on which initiate transfer. Source initiated strobe for data transfer: The block diagram and timing diagram of strobe initiated by source unit is shown in figure below:

data bus after a per determine time interval. Now, actually in computer, in the first case means in strobe initiated by source - the strobe may be a memory-write control signal from the CPU to a memory unit.The source, CPU, places the word on the data bus and informs the memory unit, which is the destination, that this is a write operation. And in the second case i.e, in the strobe initiated by destination - the strobe may be a memory read control from the CPU to a memory unit.The destination, the CPU, initiates the read operation to inform the memory, which is a source unit, to place selected word into the databus.

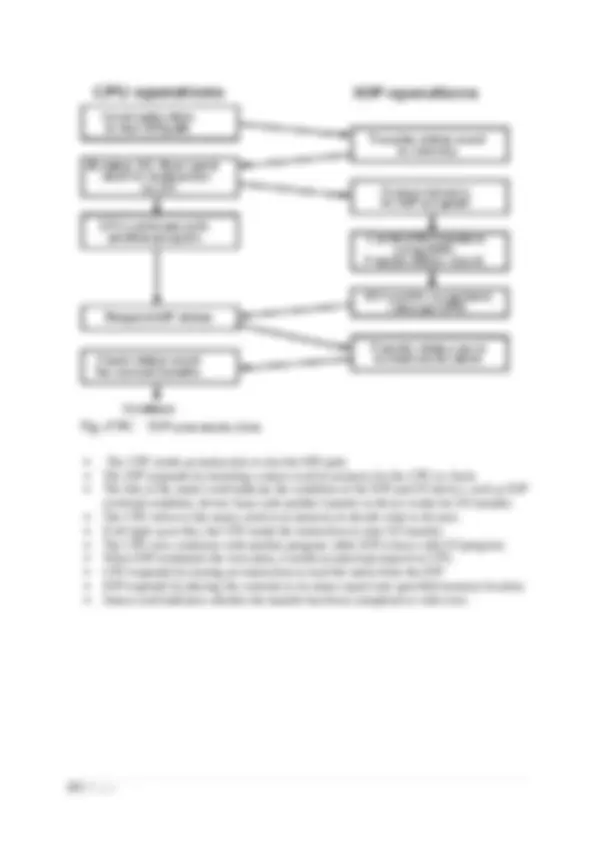

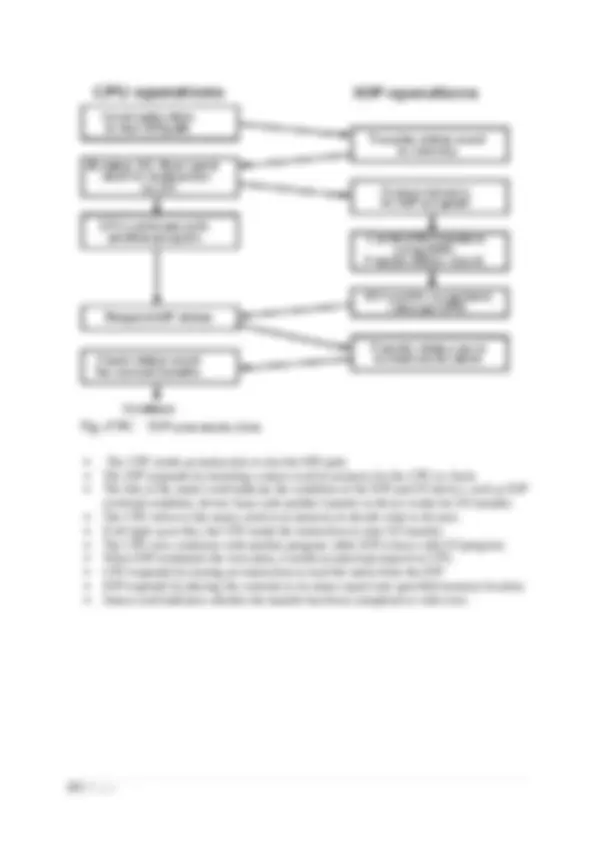

The disadvantage of strobe method is that source unit that initiates the transfer has no way of knowing whether the destination has actually received the data that was placed in the bus.Similarly, a destination unit that initiates the transfer has no way of knowing whether the source unit, has actually placed data on the bus. This problem can be solved by handshaking method. Hand shaking method introduce a second control signal line that provides a replay to the unit that initiates the transfer. In it, one control line is in the same direction as the data flow in the bus from the source to destination.It is used by source unit to inform the destination unit whether there are valid data in the bus.The other control line is in the other direction from destination to the source.It is used by the destination unit to inform the source whether it can accept data.And in it also, sequence of control depends on unit that initiate transfer.Means sequence of control depends whether transfer is initiated by source and destination.Sequence of control in both of them are described below: Source initiated Handshaking: The source initiated transfer using handshaking lines is shown in figure below:

In its block diagram, we se that two handshaking lines are "data valid", which is generated by the source unit, and "data accepted", generated by the destination unit. The timing diagram shows the timing relationship of exchange of signals between the two units.Means as shown in its timing diagram, the source initiates a transfer by placing data on the bus and enabling its data valid signal.The data accepted signal is then activated by destination unit after it accepts the data from the bus.The source unit then disable its data valid signal which invalidates the data on the bus.After this, the destination unit disables its data accepted signal and the system goes into initial state.The source unit does not send the next data item until after the destination unit shows its readiness to accept new data by disabling the data accepted signal. This sequence of events described in its sequence diagram, which shows the above sequence in which the system is present, at any given time. Destination initiated handshaking: The destination initiated transfer using handshaking lines is shown in figure below:

I/O device places the data on the I/O bus and enables its data valid signal. The interface accepts the data in the data register and sets the F bit of status register and also enables the data accepted signal. Data valid line is disables by I/O device. CPU is in a continuous monitoring of the interface in which it checks the F bit of the status register. o If it is set i.e. 1, then the CPU reads the data from data register and sets F bit to zero. o If it is reset i.e. 0, then the CPU remains monitoring the interface. Interface disables the data accepted signal and the system goes to initial state where next item of data is placed on the data bus. Characteristics: Continuous CPU involvement CPU slowed down to I/O speed Simple Least hardware

Direct Memory Access Large blocks of data transferred at a high speed to or from high speed devices, magnetic drums, disks, tapes, etc. DMA controller Interface that provides I/O transfer of data directly to and from the memory and the I/O device CPU initializes the DMA controller by sending a memory address and the number of words to be transferred Actual transfer of data is done directly between the device and memory through DMA controller -> Freeing CPU for other tasks The transfer of data between the peripheral and memory without the interaction of CPU and letting the peripheral device manage the memory bus directly is termed as Direct Memory Access (DMA). Removing the CPU from the path and letting the peripheral device manage the memory buses directly would improve the speed of transfer. This technique is known as DMA.

The two control signals Bus Request and Bus Grant are used to fascinate the DMA transfer. The bus request input is used by the DMA controller to request the CPU for the control of the buses. When BR signal is high, the CPU terminates the execution of the current instructions and then places the address, data, read and write lines to the high impedance state and sends the bus grant signal. The DMA controller now takes the control of the buses and transfers the data directly between memory and I/O without processor interaction. When the transfer is completed, the bus request signal is made low by DMA. In response to which CPU disables the bus grant and again CPU takes the control of address, data, read and write lines. The transfer of data between the memory and I/O of course facilitates in two ways which are DMA Burst and Cycle Stealing. DMA Burst : The block of data consisting a number of memory words is transferred at a time. Cycle Stealing : DMA transfers one data word at a time after which it must return control of the buses to the CPU. CPU is usually much faster than I/O (DMA), thus CPU uses the most of the memory cycles DMA Controller steals the memory cycles from CPU For those stolen cycles, CPU remains idle For those slow CPU, DMA Controller may steal most of the memory cycles which may cause CPU remain idle long time DMA Controller The DMA controller communicates with the CPU through the data bus and control lines. DMA select signal is used for selecting the controller, the register select is for selecting the register. When the bus grant signal is zero, the CPU communicates through the data bus to read or write into the DMA register. When bus grant is one, the DMA controller takes the control of buses and transfers the data between the memory and I/O. The address register specifies the desired location of the memory which is incremented after each word is transferred to the memory. The word count register holds the number of words to be transferred which is decremented after each transfer until it is zero. When it is zero, it indicates the end of transfer. After which the bus grant signal from CPU is made low and CPU returns to its normal operation. The control register specifies the mode of transfer which is Read or Write.