Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

digital circuits need to analyzed for different time periods.

Typology: Study notes

1 / 71

This page cannot be seen from the preview

Don't miss anything!

1

Note: pictures in this lecture have been taken from various websites

A mandatory step in digital design process is the analysis, determination and elimination of possible timing violations within any design’s tolerance range. This fact is becoming more important for nano scale technology and the high speed requirements where greater density of today’s MCM, SOC, NoC and ASIC designs that are pushing the limits of speed. Any design must consider the fact that component timing varies from component to component chip to chip and board to board. Each chip/board that is manufactured contains a slightly different combination of fast and slow components that can cause some timing margin. The ASIC designer must always account for these variations and check timing violation if any within the ASIC chip and in the board that contains the ASIC using worse case corner analysis.

A circuit board, MCM, SOC, ASIC … contain a variety of devices that cover the range of acceptable performance specifications. Naturally some devices will be fast and the others slow, but overall the circuit is expected to be within the specifications. Numerous factors can affect the performance of an ASIC/MCM/SOC/board such as the : Environment Factors: 1)Devices may be at different temperatures. Thus some devices will run faster than the others. 3)The layout affects the timing due to time constant of the routing area.

LOAD Condition

Delay and Timing Parameters Capacitances represent CMOS gate inputs Delay Equation Delay = [TP + K 1 ΣNi + KNi + K 2 ML ] K* TP = Intrinsic delay in (ns) K 1 = fan-out derating factor (ns / fan-out) ΣNi + KNi = Sum of input load being driven by the gate ( Equivalent unit loads) K 2 = Metal load derating factor (ns / μm) ML = Metal length being driven by the output ( μ m) K* = Composite derating factor due to process, temperature and voltage variation. IN OUT C_metal C_ gate

Input Loading Wirin g

Example

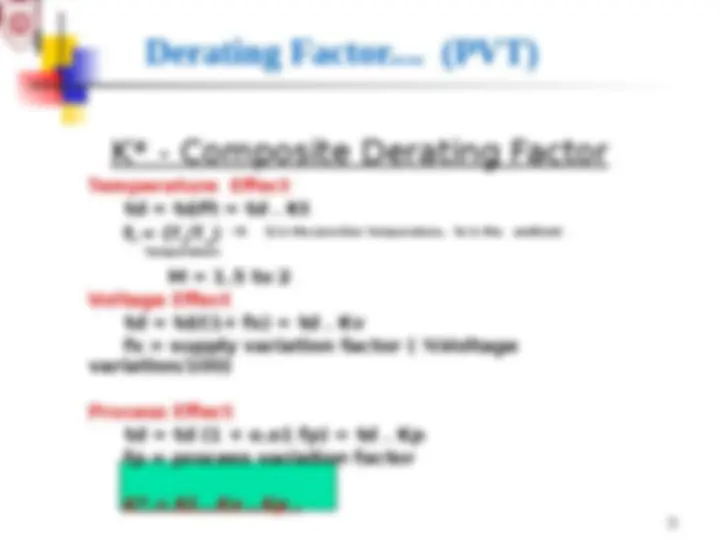

Determine the overall derating factor, K* for the following condition: ±10% voltage variation 40% process variation. (which are the factors contributing to the regions of ambiguity). Assume an ambient temperature of 25 °C. Power dissipation = 1W and chip and ceramic packaging has thermal resistance θJa=35 °C/W

= 1 / 0. = 1.11 or 11% increase

Chain propagation (ms) – 50 inverters 9 8 7 6 5 4 1 2 3 4 5 6 (^7) Process fabrication run number Process Propagation Delay Fast 14. Slow 21 Typical 18. Usually from +20 % to –20 % fluctuation i.e. 40% change Process parameters are characterized as nominal and corner: (^) The nominal process is the expected process. (^) Corner processes are the limits of acceptable process parameters.

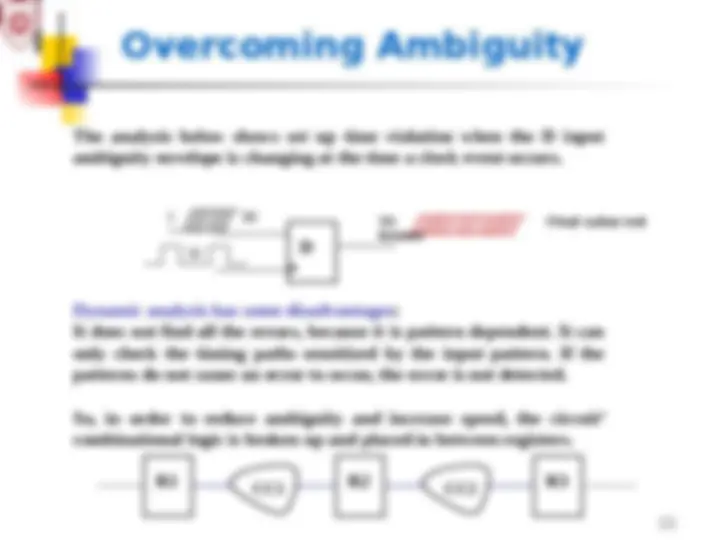

Apart from external variables discussed, the data dependent delay results from two effects:

Determine the delay experienced by the driver circuit given below with a nominal delay of Tp=1.5 ps. This is a very much simplified delay calculation to show the effects of the routing and fanout Assume 1UL(unit load) for basic inverter or 2-input NAND value e.g. 5fF D D D Tp=1.5 ns L=2.5mm 2UL 2UL 2UL D 1UL 2UL

1UL …14 UL Combined load Lets assume the following 2 constants: K1= 0.06 ns/UL delay factor per unit load connected K2= 0.08 ns/mm delay factor per unit length wire

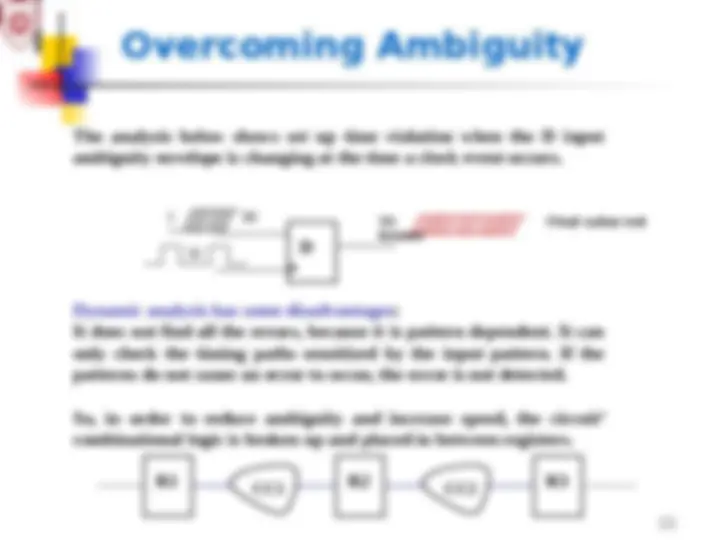

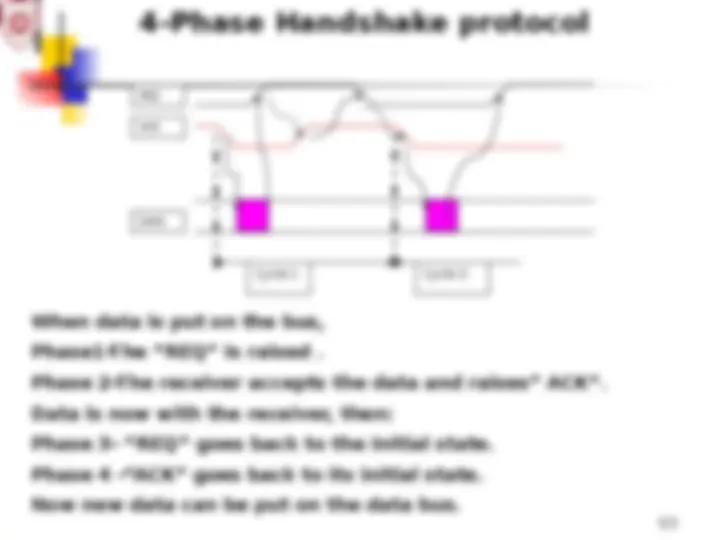

Worst Case Timing Analysis Worst case timing analysis involves determining the regions of ambiguity , or the range of time in which a state strength may change. Standard representation of the ambiguity region is by a series of signal edges close together or with a timing envelope. The beginning and end of the ambiguity region are measured with respect to a referenced event such as the clock. The diagram below shows the earliest and the latest time at which the specified signal makes the transition for ‘0’ to ‘1’. Rising signal ambiguity Envelope

Earliest arriving signal Latest arriving signal

20 If several combinational logic elements are connected serially, the ambiguity region can grow quite large, and in fact this accurately represents the results of the several worst cases combined. The case when all the components have minimum delay, and the case when all have maximum delay. 4 8 8 16 12 24 Min Max A D-type flip flop can reduce the ambiguity of a signal on its input and this is a major reason for using synchronous elements in a design. Any accumulated ambiguity on the D input is eliminated and is replaced with the combined ambiguity of the CLK input and the output. D 50 55 60

5 50